STM32 Interrupts

The Cortex-M core in STM32 features a robust exception handling system. It categorizes events that can interrupt the current execution into two types: exceptions and interrupts. Exceptions are managed by the kernel, while external interrupts are handled separately. These are organized into two tables, numbered from 0 to 15, known as kernel exceptions, and numbers 16 and above are referred to as external interrupts. This structure is called the interrupt vector table.

In STM32, the vector table is reorganized. The exceptions numbered from -3 to 6 are considered system exceptions, such as reset, NMI (Non-Maskable Interrupt), and HardFault. These kernel exceptions cannot be prioritized or masked. Starting from number 7, the interrupts are classified as external, and their priorities can be configured by the user.

Given the large number of interrupts available on STM32, manual configuration can be complex. To simplify this, the NVIC (Nested Vectored Interrupt Controller) is used. It is an integral part of the Cortex-M core and provides a powerful way to manage interrupt priorities and enable/disable settings.

**STM32 Interrupt Configuration**

To configure STM32 interrupts, you need to understand two key concepts and set four variables.

**Four Variables:**

- `NVIC_IRQChannel`: Specifies the interrupt vector.

- `NVIC_IRQChannelCmd`: Enables or disables the interrupt.

- `NVIC_IRQChannelPreemptionPriority`: Sets the preemption priority.

- `NVIC_IRQChannelSubPriority`: Sets the response priority.

**Two Key Concepts:**

- **Preemption Priority**: Determines whether one interrupt can interrupt another. A lower numerical value means higher priority. For example, if interrupt A has a lower preemption priority than interrupt B, it can preempt B during execution.

- **Response Priority**: Used when preemption priorities are equal. If two interrupts occur at the same time, the one with the higher response priority (lower numerical value) will be processed first.

**STM32 Interrupt Configuration**

To configure STM32 interrupts, you need to understand two key concepts and set four variables.

**Four Variables:**

- `NVIC_IRQChannel`: Specifies the interrupt vector.

- `NVIC_IRQChannelCmd`: Enables or disables the interrupt.

- `NVIC_IRQChannelPreemptionPriority`: Sets the preemption priority.

- `NVIC_IRQChannelSubPriority`: Sets the response priority.

**Two Key Concepts:**

- **Preemption Priority**: Determines whether one interrupt can interrupt another. A lower numerical value means higher priority. For example, if interrupt A has a lower preemption priority than interrupt B, it can preempt B during execution.

- **Response Priority**: Used when preemption priorities are equal. If two interrupts occur at the same time, the one with the higher response priority (lower numerical value) will be processed first.

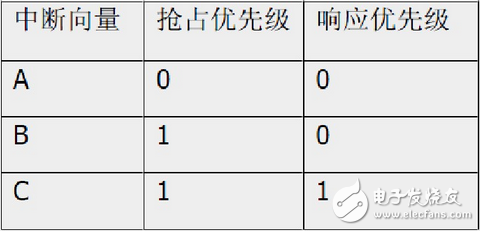

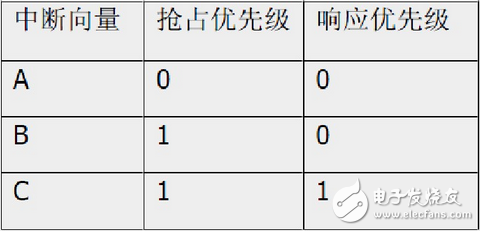

For instance, if the kernel is executing an interrupt service function C, it can be interrupted by an interrupt A with a higher preemption priority. However, if B and C have the same preemption priority, B cannot interrupt C. But if both B and C arrive simultaneously, the system will handle B first due to its higher response priority.

The number of preemption and response priority levels depends on how the 4-bit priority grouping is configured. Here are the common groups:

- **Group 0**: All 4 bits are used for preemption priority. There are 16 levels, no response priority.

- **Group 1**: 1 bit for preemption, 3 bits for response. Preemption levels: 0–1; Response levels: 0–7.

- **Group 2**: 2 bits for preemption, 2 bits for response. Preemption levels: 0–3; Response levels: 0–3.

- **Group 3**: 3 bits for preemption, 1 bit for response. Preemption levels: 0–7; Response levels: 0–1.

- **Group 4**: All 4 bits for response priority. No preemption priority.

**STM32 Interrupt Configuration Method**

1. Define an interrupt configuration structure variable:

```c

NVIC_InitTypeDef NVIC_InitStruct;

```

2. Set the priority grouping:

```c

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);

```

3. Initialize the structure:

- Set the interrupt vector (`NVIC_IRQChannel`).

- Enable or disable the interrupt (`NVIC_IRQChannelCmd`).

- Assign preemption priority (`NVIC_IRQChannelPreemptionPriority`).

- Assign response priority (`NVIC_IRQChannelSubPriority`).

4. Apply the configuration:

```c

NVIC_Init(&NVIC_InitStruct);

```

This process allows developers to efficiently manage and prioritize interrupts, ensuring smooth and responsive system behavior.

For instance, if the kernel is executing an interrupt service function C, it can be interrupted by an interrupt A with a higher preemption priority. However, if B and C have the same preemption priority, B cannot interrupt C. But if both B and C arrive simultaneously, the system will handle B first due to its higher response priority.

The number of preemption and response priority levels depends on how the 4-bit priority grouping is configured. Here are the common groups:

- **Group 0**: All 4 bits are used for preemption priority. There are 16 levels, no response priority.

- **Group 1**: 1 bit for preemption, 3 bits for response. Preemption levels: 0–1; Response levels: 0–7.

- **Group 2**: 2 bits for preemption, 2 bits for response. Preemption levels: 0–3; Response levels: 0–3.

- **Group 3**: 3 bits for preemption, 1 bit for response. Preemption levels: 0–7; Response levels: 0–1.

- **Group 4**: All 4 bits for response priority. No preemption priority.

**STM32 Interrupt Configuration Method**

1. Define an interrupt configuration structure variable:

```c

NVIC_InitTypeDef NVIC_InitStruct;

```

2. Set the priority grouping:

```c

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);

```

3. Initialize the structure:

- Set the interrupt vector (`NVIC_IRQChannel`).

- Enable or disable the interrupt (`NVIC_IRQChannelCmd`).

- Assign preemption priority (`NVIC_IRQChannelPreemptionPriority`).

- Assign response priority (`NVIC_IRQChannelSubPriority`).

4. Apply the configuration:

```c

NVIC_Init(&NVIC_InitStruct);

```

This process allows developers to efficiently manage and prioritize interrupts, ensuring smooth and responsive system behavior.

**STM32 Interrupt Configuration**

To configure STM32 interrupts, you need to understand two key concepts and set four variables.

**Four Variables:**

- `NVIC_IRQChannel`: Specifies the interrupt vector.

- `NVIC_IRQChannelCmd`: Enables or disables the interrupt.

- `NVIC_IRQChannelPreemptionPriority`: Sets the preemption priority.

- `NVIC_IRQChannelSubPriority`: Sets the response priority.

**Two Key Concepts:**

- **Preemption Priority**: Determines whether one interrupt can interrupt another. A lower numerical value means higher priority. For example, if interrupt A has a lower preemption priority than interrupt B, it can preempt B during execution.

- **Response Priority**: Used when preemption priorities are equal. If two interrupts occur at the same time, the one with the higher response priority (lower numerical value) will be processed first.

**STM32 Interrupt Configuration**

To configure STM32 interrupts, you need to understand two key concepts and set four variables.

**Four Variables:**

- `NVIC_IRQChannel`: Specifies the interrupt vector.

- `NVIC_IRQChannelCmd`: Enables or disables the interrupt.

- `NVIC_IRQChannelPreemptionPriority`: Sets the preemption priority.

- `NVIC_IRQChannelSubPriority`: Sets the response priority.

**Two Key Concepts:**

- **Preemption Priority**: Determines whether one interrupt can interrupt another. A lower numerical value means higher priority. For example, if interrupt A has a lower preemption priority than interrupt B, it can preempt B during execution.

- **Response Priority**: Used when preemption priorities are equal. If two interrupts occur at the same time, the one with the higher response priority (lower numerical value) will be processed first.

For instance, if the kernel is executing an interrupt service function C, it can be interrupted by an interrupt A with a higher preemption priority. However, if B and C have the same preemption priority, B cannot interrupt C. But if both B and C arrive simultaneously, the system will handle B first due to its higher response priority.

The number of preemption and response priority levels depends on how the 4-bit priority grouping is configured. Here are the common groups:

- **Group 0**: All 4 bits are used for preemption priority. There are 16 levels, no response priority.

- **Group 1**: 1 bit for preemption, 3 bits for response. Preemption levels: 0–1; Response levels: 0–7.

- **Group 2**: 2 bits for preemption, 2 bits for response. Preemption levels: 0–3; Response levels: 0–3.

- **Group 3**: 3 bits for preemption, 1 bit for response. Preemption levels: 0–7; Response levels: 0–1.

- **Group 4**: All 4 bits for response priority. No preemption priority.

**STM32 Interrupt Configuration Method**

1. Define an interrupt configuration structure variable:

```c

NVIC_InitTypeDef NVIC_InitStruct;

```

2. Set the priority grouping:

```c

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);

```

3. Initialize the structure:

- Set the interrupt vector (`NVIC_IRQChannel`).

- Enable or disable the interrupt (`NVIC_IRQChannelCmd`).

- Assign preemption priority (`NVIC_IRQChannelPreemptionPriority`).

- Assign response priority (`NVIC_IRQChannelSubPriority`).

4. Apply the configuration:

```c

NVIC_Init(&NVIC_InitStruct);

```

This process allows developers to efficiently manage and prioritize interrupts, ensuring smooth and responsive system behavior.

For instance, if the kernel is executing an interrupt service function C, it can be interrupted by an interrupt A with a higher preemption priority. However, if B and C have the same preemption priority, B cannot interrupt C. But if both B and C arrive simultaneously, the system will handle B first due to its higher response priority.

The number of preemption and response priority levels depends on how the 4-bit priority grouping is configured. Here are the common groups:

- **Group 0**: All 4 bits are used for preemption priority. There are 16 levels, no response priority.

- **Group 1**: 1 bit for preemption, 3 bits for response. Preemption levels: 0–1; Response levels: 0–7.

- **Group 2**: 2 bits for preemption, 2 bits for response. Preemption levels: 0–3; Response levels: 0–3.

- **Group 3**: 3 bits for preemption, 1 bit for response. Preemption levels: 0–7; Response levels: 0–1.

- **Group 4**: All 4 bits for response priority. No preemption priority.

**STM32 Interrupt Configuration Method**

1. Define an interrupt configuration structure variable:

```c

NVIC_InitTypeDef NVIC_InitStruct;

```

2. Set the priority grouping:

```c

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);

```

3. Initialize the structure:

- Set the interrupt vector (`NVIC_IRQChannel`).

- Enable or disable the interrupt (`NVIC_IRQChannelCmd`).

- Assign preemption priority (`NVIC_IRQChannelPreemptionPriority`).

- Assign response priority (`NVIC_IRQChannelSubPriority`).

4. Apply the configuration:

```c

NVIC_Init(&NVIC_InitStruct);

```

This process allows developers to efficiently manage and prioritize interrupts, ensuring smooth and responsive system behavior.coin battery holder,cr2032 battery holder,cr2032 holder,cr2032 socket,cr2450 battery holder,cr2450 holder,2450 battery holder

Dongguan Yiyou Electronic Technology Co., Ltd. , https://www.dsubminiature.com