Serial interconnects form the key foundation of modern communication systems , so the choice of serializer / deserializer (SerDes) can have a significant impact on system cost and performance. Despite traditional data-based communication The SerDes cater for the appropriate byte (byte-oriented) oriented, packet-based (packet-based) design of the bus, but many other telecommunication applications bus format. This makes it difficult to design the SerDes technology into these systems. This article summarizes the SerDes architecture, and displays a description of how a particular architecture suitable for telecommunications signal processing system.

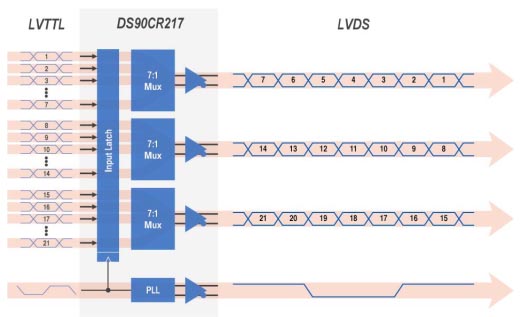

SerDes Architecture: OverviewThe parallel clock SerDes serializes the parallel wide bus into multiple differential signal pairs, transmitting a clock in parallel with the data. These SerDes are relatively inexpensive and can effectively extend the wide bus through cables or backplanes in applications that typically require multiple SerDes simultaneously .

Figure 1. DS90CR217 21 -bit channel-link parallel clock serializer

Input latch | Input latch |

Mux | Multiplexer |

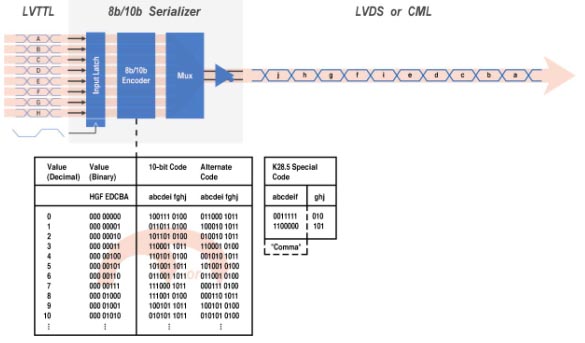

8b/10b SerDes maps each data byte to a 10 -bit code and serializes it into a single signal pair. The 10 -bit code is defined as follows: Provides sufficient conversion for receiver clock recovery and guarantees DC balance (sends an equal number of "1"s and "0"s). These attributes enable 8b/10b SerDes to operate at high speeds with low signal distortion on lossy interconnects and fiber optic cables.

Figure 2. Block diagram of the 8b/10b serializer

8b/10b serializer | 8b/10b serializer |

LVDS or CML | LVDS or CML |

Input latch | Input latch |

8b/10b encoder | 8b/10b encoder |

Mux | Multiplexer |

Value(decimal) | Value ( decimal ) |

Value(binary) | Value ( binary ) |

10-bit code | 10 -bit code |

Alternate code | Optional code |

K28.5 special code | K28.5 special code |

Comma | comma |

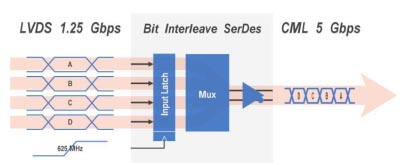

Bit-interleaved SerDes aggregates bits in multiple input serial streams into faster serial signal pairs. This type of SerDes maximizes throughput with minimal cabling.

Â

Figure 3. Block diagram of a bit interleaved serializer.

Bit interleave SerDes | Bit interleaved SerDes |

Input latch | Input latch |

Mux | Multiplexer |

Â

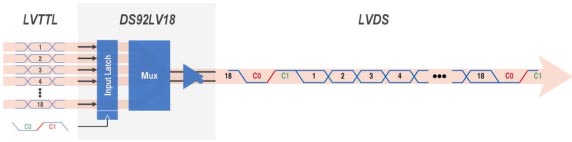

Figure 4. DS92LV18 18 -Bit Bus LVDS Embedded Clock for Serializer

Input latch | Input latch |

Mux | Multiplexer |

The embedded clock bit architecture serializes the data bus and clock into a serial signal pair. Two clock bits, one low and one high, embed a serial data stream in each clock cycle, framing the start and end of each serialized word (hence, the name of the alternative is " Start - end bit " SerDes " and create a periodic rising edge in the serial stream. Since the payload is sandwiched between embedded clock bits, the data payload word width is not limited to a multiple of the byte. In fact, 10 and 18 -bit bus products are available. Â

Â

Figure 5. Regular embedded clock bit conversion.

Period embedded clock transiTIon | Regular embedded clock bit conversion |

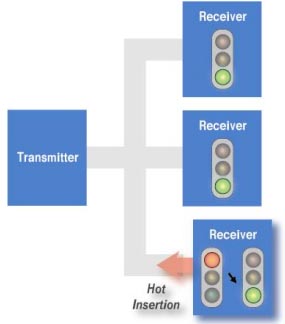

After power up, the receiver automatically searches for the rising edge of the regular embedded clock. Because the data bits of the data payload change values ​​over time, but the clock bits do not change over time, the receiver can locate and synchronize with unique clock edges. After locking, the receiver recovers data from the serial stream, regardless of the payload data pattern. This automatic synchronization feature is often referred to as "lock to random data" and requires no external system intervention. This is a particularly useful feature in systems where the receiver is located in a remote module that is not directly controlled by the system, and in which one of the transmitters broadcasts to multiple receivers. In the case of broadcast, the new receiver module plugged into the bus will lock to random data without having to send communication mode or characters to interrupt communication to other receivers.

Figure 6. The receiver automatically locks to random data during hot insertion.

Transmitter | Transmitter |

Receiver | receiver |

Hot inserTIon | Hot insertion |

Most SerDes rely on tight control of the jitter of the transmit and receive clocks for lock and lock monitoring. However, the embedded clock bit receiver synchronizes the incoming rising edge of the embedded clock and requires the receiver reference clock only during initial synchronization to prevent locking to false harmonics. This can loosen the jitter requirements of the transmit and reference clocks by at least an order of magnitude. In fact, the receiver reference clock only needs to be at the transmit clock frequency. Within ± 50,000 PPM . This can save a lot of money in systems that use non-standard oscillators because standard frequencies that are very low cost can be used.

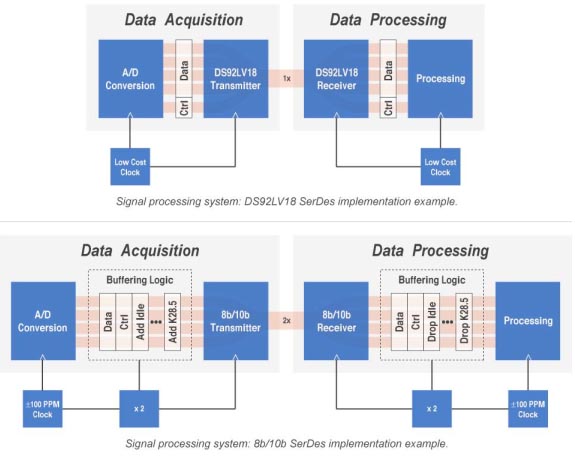

System comparisonThe embedded clock bit SerDes is especially useful for applications that send raw data as well as control, parity, frames, status, and more. For example, base station, automotive image/video and sensor signal processing systems where an analog/digital converter, camera or display passes raw data to a signal processing unit at the other end of the link. To illustrate, assume that the use of National Semiconductor's Data Acquisition System DS92LV18 in FIG. 7. Here, the DS92LV18 not only serializes the data, but also serializes two additional pieces of information, such as parity, status bits, and so on. These bits are serialized with the data bits at the normal A/D sampling rate, eliminating the need for data buffering or additional logic.

Figure 7. Example implementation of a signal processing system based on DS92LV18 SerDes ( above ) and 8b/10b SerDes ( below ) .

Data acquisiTIon | data collection |

A/D conversion | A/D conversion |

Data | data |

Ctrl | control |

Transmitter | Transmitter |

Low cost clock | Low cost clock |

Data processing | data processing |

Processing | deal with |

Signal processing system: DS92LV18 SerDes implemenTIon example. | Signal Processing System : DS92LV18 SerDes implementation example. |

Buffering logic | Buffer logic |

Add idle | Cable Tray Connectors

Cable tray connectors are an essential component in cable management systems. They are used to connect different sections of cable trays together, allowing for the safe and efficient routing of cables throughout a building or industrial facility. In this article, we will provide a comprehensive overview of cable tray connectors, including their types, materials, and applications. Cable Tray Connectors,Aluminum Support Connectors,Aluminum Splice Connectors,Support Cable Trays Rayhot Technology Group Co.,Ltd , https://www.cnrayhot.com |