Due to the high cost of the ASIC solution NRE, the product development cycle is long and there is insufficient flexibility in supporting the upgrade of various wireless standards. FPGA power consumption is higher than ASIC and DSP accelerators for high-speed, complex operations, and it is difficult to achieve ideal conditions for rapid development and debugging. Based on this, TI's recently introduced DSP solution SoC architecture for wireless infrastructure applications, based on C64x+ multi-core DSP, combines ASIC processing power with FPGA flexibility to accommodate 3G and 4G wireless infrastructure equipment manufacturers for high-performance chips. demand.

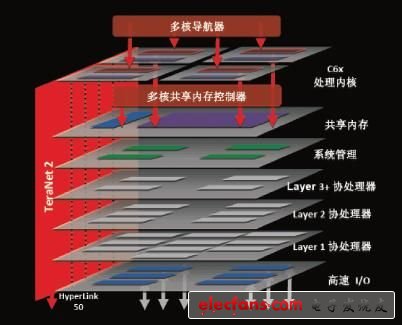

The highly flexible programmable solution, combined with the optimization features of the ASIC solution, is TI's next-generation DSP multicore architecture for the wireless infrastructure market. Key features of the new DSP architecture based on 40nm process include: multi-core DSP can achieve 1.2GHz working frequency; increased floating point supports 4G multi-variable control system development, can easily realize support for time division and crossover system; new multi-core navigator It can realize the accurate transfer of data between DSP core and hardware accelerator, and provide non-blocking switch architecture peripherals with 50Gbps, which can meet the requirements of future 4G systems without using system modules; stable tool suite, application-specific software library and Platform software that provides users with more efficient debugging and analysis for shorter development cycles; TI's new DSP architecture running at up to 1.2GHz with engine performance of 256 GMACS and 128 GFLOPS achieves a 5x improvement in DMS performance while increasing average kernel storage 2 times, to ensure the stability of application performance; provide high-performance layer 1 and layer 2 network coprocessor.

The new SoC architecture multi-core navigator (MulTIcore Navigator), which uses the 8192 task-based queue to optimize the on-chip network management unit of the data stream, supports direct communication between the core and memory access, eliminating peripheral access and fully releasing multi-core performance. . The program model is greatly simplified by extracting many details that may affect software development in multi-core systems. Since each DSP core integrates fixed-point and floating-point processing functions, each core can work independently of each other without being affected by inter-core collisions by providing automatic path settings between cores, hardware accelerators, and peripherals. The design engineer saved three months. The multi-core shared memory controller design accelerates on-chip and external memory access speeds; the new architecture also supports dynamic system scheduling between cores and supports full-core licensing, making multi-core architectures similar to powerful single-core systems.

These are 4-core devices for wireless base stations, as well as 8-core devices for media gateways and networking applications. TI is expected to begin sampling in the second half of 2010.

PTFE caoted open mesh belting products are used in drying applications where air flow is required.Typical applications include screen print and textile dryers, non-wovens processing and similar processes that require the circulation of hot air.

Our open mesh belting combines a maximum amount of open area with good mechanical strength, which maximize the rate of drying.

Open Mesh Belt,PTFE Mesh Conveyor Belt,Mesh Conveyor Belt,PTFE Coated Open Mesh Fabrics

TAIZHOU YAXING PLASTIC INDUSTRY CO., LTD , https://www.yaxingptfe.com