摘è¦ï¼šä¸ºäº†è§£å†³æŸäº›é¢†åŸŸå¯¹è§†é¢‘实时处ç†ç³»ç»Ÿå·¥ä½œæ¸©åº¦èŒƒå›´è¦æ±‚较高的问题,设计了基于TMS320DM642å’ŒADV7179的视频实时处ç†å’Œæ˜¾ç¤ºç³»ç»Ÿï¼ŒåŒ…括系统硬件和基于DSPï¼BIOS的软件系统的设计。åŒæ—¶è¿˜æ出了一ç§é‡‡ç”¨TMS320DM642 GPIO接å£æŽ¥æ”¶MPEG-2ä¼ è¾“æµ(TS)的方案。实验结果较好地验è¯äº†è®¾è®¡çš„åˆç†æ€§å’Œæ£ç¡®æ€§ã€‚

关键è¯ï¼šTMS320DM642ï¼›ADV7179;视频处ç†ï¼›è§†é¢‘显示

引言

éšç€ç”µå技术的å‘展,数å—ä¿¡å·å¤„ç†å™¨çš„应用越æ¥è¶Šå¹¿æ³›ã€‚涉åŠçš„应用领域大到航空航天器æ,如飞机ã€é£žèˆ¹ç‰ï¼›å°åˆ°æ—¥å¸¸ç”µå产å“,如手机ã€æ•°ç 相机ã€MP4ã€å¤šåª’体和通信设备ç‰ã€‚TMS320DM642(以下简称DM642)是TIå…¬å¸æŽ¨å‡ºçš„一款32ä½å®šç‚¹DSP芯片,主è¦é¢å‘æ•°å—媒体,特别适åˆäºŽéŸ³è§†é¢‘ä¿¡å·çš„处ç†ã€‚

然而目å‰å›½å†…基于DM642的视频显示方案大多采用飞利浦公å¸çš„SAA71XX系列视频编ç 芯片,而这些芯片的工作温度都ä¸èƒ½æ»¡è¶³æ ‡å‡†T业温度范围(-40~+85℃)。本文æ出的方案采用的全部芯片的工作温度范围å‡èƒ½æ»¡è¶³å·¥ä¸šæ¸©åº¦æ ‡å‡†ï¼Œå› æ¤å…·æœ‰æ›´å¹¿æ³›çš„适用环境。

1 DM642结构特点

DM642ä¿ç•™äº†C64xåŽŸæœ‰çš„å†…æ ¸ç»“æž„ï¼Œå·¥ä½œé¢‘çŽ‡ç”±å†…éƒ¨å€é¢‘器设置,å¯ä»¥è¾¾åˆ°500 MHzã€600 MHzå’Œ720MHz。相应的时钟周期为2 nsã€1.67 nså’Œ1.39 ns。æ¯ç§’å¯æ‰§è¡ŒæŒ‡ä»¤æ•°ä¸º4 000 MIPSã€4 800 MIPSå’Œ5 760 MIPS。DM642采用TIå…¬å¸ç¬¬äºŒä»£å¢žå¼ºåž‹è¶…长指令集(VelociTI.2),它的EMIFA接å£æ•°æ®æ€»çº¿å®½åº¦ä¸º64ä½ï¼Œæœ€é«˜æ•°æ®å˜å–频率为133 MHz,å¯ç›´æŽ¥ä¸Žå¤§å®¹é‡ã€ä½Žæˆæœ¬çš„SDRAMèŠ¯ç‰‡æ— ç¼è¿žæŽ¥ã€‚DM642片上带有3个åŒé€šé“æ•°å—视频接å£ï¼Œå¯åŒæ—¶å¤„ç†å¤šè·¯æ•°å—视频æµã€‚

TMS320DM642的片上å˜å‚¨ç©ºé—´åˆ†ä¸ºL1å˜å‚¨åŒºå’ŒL2å˜å‚¨åŒºä¸¤éƒ¨åˆ†ã€‚L1å˜å‚¨åŒºåˆåˆ†ä¸ºç¨‹åºå˜å‚¨ç©ºé—´å’Œæ•°æ®å˜å‚¨ç©ºé—´ï¼Œç¨‹åºå˜å‚¨ç©ºé—´å’Œæ•°æ®å˜å‚¨ç©ºé—´çš„容é‡å‡ä¸º16K×8ä½ï¼›L2å˜å‚¨åŒºä¸ºå•ä¸€çš„RAM,其容é‡ä¸º256K×8ä½ï¼ŒL2å˜å‚¨åŒºç®¡ç†å¤–部扩展的数æ®å˜å‚¨å™¨å’Œç¨‹åºå˜å‚¨å™¨ã€‚

2 ADV7179硬件特性

ADV7179是ADIå…¬å¸ç”Ÿäº§çš„一款数å—视频编ç 芯片,它能将8ä½CCIR-601 4:2:2æ ¼å¼çš„æ•°å—视频信å·åˆ†é‡è½¬æ¢ä¸ºæ ‡å‡†çš„模拟基带电视信å·ã€‚ADV7179是一款高性能ã€å°å°ºå¯¸çš„芯片,40引脚的LFCSPå°è£…大å°ä»…为6 mm×6 mm,而且具有出色的APM(Advanced Power Management,高级电æºç®¡ç†)功能,特别适åˆåº”用于手机ã€æ•°ç 相机åŠæ‰‹æŒè§†é¢‘设备上。ADV7179å…·æœ‰æ ‡å‡†I2C总线接å£ï¼Œæ”¯æŒI2C总线快速通信模å¼ï¼Œèƒ½é€šè¿‡ä¸»æœºå¯¹å…¶è¿›è¡Œæ–¹ä¾¿çš„é…置。ADV7179具有3个å¯ç¼–程控制的高性能10ä½è§†é¢‘DAC,å¯åˆ†åˆ«è¾“出CVBSã€Yï¼C或RGBä¿¡å·ï¼Œä¸ºäº†èŠ‚çœåŠŸçŽ‡æ¶ˆè€—,å¯å…³é—DACä¸çš„ä¸€ä¸ªæˆ–å‡ ä¸ªã€‚ADV7179的工作电压å¯é€‰2.8 V或3.3 V,在两ç§å·¥ä½œç”µåŽ‹ä¸‹çš„工作温度分别å¯è¾¾-20~+85℃和-40~+85â„ƒï¼Œå› æ¤ADV7179å¯åº”用在温度è¦æ±‚较高的场åˆã€‚

3 硬件设计

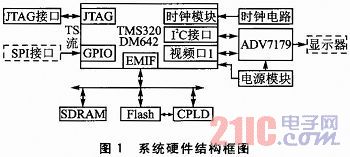

本设计的系统硬件结构框图如图1所示。其ä¸è™šçº¿æ¡†éƒ¨åˆ†ä¸ºæœ¬ç³»ç»Ÿæ‰€éœ€å¤–接的硬件资æºã€‚DM642çš„GPIO模å—接收从外部SPI接å£è¾“入的视频TSæµï¼Œå¹¶å°†å…¶å˜å‚¨åœ¨å¤–部SDRAMä¸ä»¥å¾…处ç†ã€‚DSP按帧读å–SDRAMä¸çš„TSæµæ•°æ®ï¼Œè¿›è¡Œè§£å¤ç”¨å’Œè§£åŽ‹ç¼©ï¼Œè¾“出BT656æ ¼å¼çš„视频数æ®åˆ°ADV717 9。ADV7179将接收到的视频数æ®è¿›è¡ŒDï¼A转æ¢ç¼–ç ,输出PALï¼NTSC制的模拟视频信å·åˆ°æ˜¾ç¤ºå™¨ã€‚

本文引用地å€: http://

3.1 时钟模å—

本系统时钟æºé€‰æ‹©äº†50 MHz的高精度有æºæ™¶æŒ¯ï¼Œæ™¶æŒ¯è¾“出的时钟信å·ç»æ—¶é’Ÿç¼“冲器芯片ICS551åŽä¸ºDM642æ供时钟。设计ä¸DM642çš„CLKMODE1å’ŒCLKMODE0å¼•è„šåˆ†åˆ«æŽ¥é«˜ç”µå¹³å’Œä½Žç”µå¹³ï¼Œå› æ¤DSPå€é¢‘å› å设置æˆ12,å³DM642的工作主频为50 MHz×12=600 MHz。å¦ä¸€æ–¹é¢ï¼Œä¸ºäº†ç»™EMIF接å£æ‰©å±•SDRAMæ供备用时钟方案,设计了备用时钟电路。25 MHzé«˜ç²¾åº¦æ— æºæ™¶æŒ¯è¾“出的时钟信å·è¾“入钟乘法器ICS512,通过对ICS512çš„S1ã€S0引脚高低电平的ä¸åŒè®¾ç½®ï¼Œå¯ä»¥å¾—到125MHzã€133.33 MHzã€150 MHzç‰ä¸åŒé¢‘率的时钟信å·ï¼Œä½œä¸ºEMIF接å£çš„备用åŒæ¥æ—¶é’Ÿé€‰æ‹©ã€‚本设计采用1ï¼4×CPU时钟作为EMIF接å£çš„åŒæ¥æ—¶é’Ÿã€‚

3.2 GPIO接收模å—

DM642共有16个GPIO引脚,引脚的输入ï¼è¾“出方å‘(输入ï¼è¾“出ï¼é«˜é˜»)å¯ä»¥é€šè¿‡ç¼–程设置。GPIO接å£éƒ¨åˆ†è¾“å…¥ï¼è¾“出引脚与其他接å£å¼•è„šå¤ç”¨ï¼Œå¯é€šè¿‡è®¾ç½®ç›¸å…³å¯„å˜å™¨çš„值确定å„GPIO引脚的工作方å¼ã€‚本设计采用DSP 16个GPIO引脚ä¸çš„11个接收外部SPI接å£ä¼ æ¥çš„TSæµæ•°æ®ã€‚

SPI接å£æ˜¯MPEG-2视频ç æµä¼ 输接å£æ ‡å‡†ä¹‹ä¸€ï¼Œå…±11ä½å¹¶è¡Œä¿¡å·ï¼Œå¤„ç†ç®€å•ä¸”扩展性强,目å‰ä¸€èˆ¬çš„MPEG-2视频编ç 器的输出和视频解ç å™¨çš„è¾“å…¥éƒ½æ˜¯æ ‡å‡†çš„SPI接å£ä¿¡å·ã€‚å¹¶è¡Œä¼ è¾“ç³»ç»ŸSPI包括1ä½æ—¶é’Ÿä¿¡å·ã€8ä½æ•°æ®ä¿¡å·ã€1ä½å¸§åŒæ¥ä¿¡å·å’Œ1ä½æ•°æ®æœ‰æ•ˆä¿¡å·ã€‚帧åŒæ¥ä¿¡å·å¯¹åº”TS包的åŒæ¥å—节为047H,数æ®æœ‰æ•ˆä¿¡å·ç”¨æ¥åŒºåˆ†TS包的长度为188个å—节或204个å—节。当TS包长188å—节时,数æ®æœ‰æ•ˆä¿¡å·ä¸€ç›´ä¸ºé«˜ç”µå¹³ï¼ŒåŒæ—¶æ‰€æœ‰ä¿¡å·éƒ½ä¸Žæ—¶é’Ÿä¿¡å·ä¿æŒåŒæ¥ã€‚

3.3 外部å˜å‚¨å™¨æ¨¡å—

外部å˜å‚¨å™¨åŒ…括2片128 Mbçš„SDRAM和一片4 MBçš„Flash芯片,这3片å˜å‚¨èŠ¯ç‰‡éƒ½è¿žæŽ¥åœ¨DM642çš„64ä½å¤–部å˜å‚¨æŽ¥å£(EMIF)上。

SDRAM选用的是Micronå…¬å¸çš„MT48LC4M3282,这ç§å†…å˜é¢—粒的架构为1M×32ä½Ã—4,å³æ¯ç‰‡èŠ¯ç‰‡æœ‰4个bank,æ¯bank行地å€æ•°ä¸º12(A0~A11),列地å€æ•°ä¸º8(A0~A7)。2片32ä½çš„SDRAM扩展æˆ64ä½ï¼Œä¸”æ˜ å°„åœ¨EMIFçš„CE0空间。SDRAM的时钟由EMIF接å£çš„AECLOUT1引脚æ供,本设计ä¸CPU主频采用600MHz,AECLOUT1输出é…置为4分频的DSP主频时钟,å³150MHz。

DM642ç‰‡å†…æ— é›†æˆFlash或EEPROM,系统掉电åŽå…¶å†…部å˜å‚¨å™¨å’Œå¤–部SDRAMä¸çš„程åºå’Œæ•°æ®å°†ä¼šå…¨éƒ¨ä¸¢å¤±ï¼Œå› æ¤DM642外部需è¦æ‰©å±•Flashå˜å‚¨å™¨ï¼Œç”¨æ¥å˜å‚¨ç¨‹åºå’Œé‡è¦çš„æ•°æ®ã€‚本设计ä¸Flash芯片选用的是AMDå…¬å¸çš„32 Mb(4M×8ä½)异æ¥å˜å‚¨å™¨AM29LV033C。由于DM642çš„EMIF接å£æ”¯æŒå¼‚æ¥å˜å‚¨å™¨ï¼Œå› æ¤å¯ç›´æŽ¥ä¸ŽFlash相连。AM29LV033C内部的å˜å‚¨ç©ºé—´æ˜¯åˆ†é¡µçš„,共划分为64个大å°ä¸º64 KB的扇区,通过地å€çº¿é€‰æ‹©ä¸åŒçš„扇区。AM29LV033C芯片有A[0:21]å…±22æ¡åœ°å€çº¿ï¼Œä½†æ˜¯DM642总共åªæœ‰20æ¡åœ°å€çº¿(AEA[3:22]),由于二者地å€çº¿æ•°é‡ä¸åŒï¼ŒDM642ä¸èƒ½é历Flash的所有地å€å•å…ƒã€‚为了解决这个问题,在系统ä¸é‡‡ç”¨CPLD对Flash进行页选控制。CPLD利用从DM642输入的空间片选信å·ACE1ã€é«˜ä½åœ°å€ä¿¡å·EA22ã€è¯»å†™æŽ§åˆ¶ä¿¡å·å’Œè¾“出使能控制信å·ï¼Œç»é€»è¾‘è¿ç®—输出页选控制信å·FLASH_EXT[19:21],FLASH_EXT[19:21]接Flash的最高3ä½åœ°å€çº¿ï¼Œæ¤3路信å·æŠŠFlashå˜å‚¨å™¨åˆ’分为8个页,æ¯é¡µå˜å‚¨å™¨åŒ…å«8个扇区。

3.4 I2C总线接å£

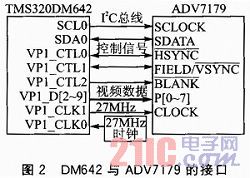

DM642集æˆæœ‰I2C总线接å£ï¼Œç”¨äºŽä¸ŽI2C总线外设通信。本设计ä¸DM642就是通过I2C总线模å—对ADV7179进行é…置的。TMS320DM642çš„I2C总线接å£åŒ…括13个寄å˜å™¨ï¼Œåˆ†åˆ«ä¸ºI2C总线时钟分频寄å˜å™¨I2CCLKHåŠI2CCLKLã€æ•°æ®è®¡æ•°å¯„å˜å™¨I2CCNTã€æ•°æ®æŽ¥æ”¶å¯„å˜å™¨I2CDRRã€æ•°æ®å‘é€å¯„å˜å™¨I2CDXRã€ä¸æ–使能寄å˜å™¨I2CIERã€ä¸æ–æºå¯„å˜å™¨I2CISRã€æ¨¡å¼å¯„å˜å™¨I2CMDRã€ä¸»åœ°å€å¯„å˜å™¨I2COARã€è®¾å¤‡ID寄å˜å™¨I2CPIDã€é¢„分频寄å˜å™¨I2CPSCã€ä»Žåœ°å€å¯„å˜å™¨I2CSAR和状æ€å¯„å˜å™¨I2CSTR。通过对这些寄å˜å™¨è¿›è¡Œç›¸åº”的读写æ“作å³å¯å®Œæˆå’ŒADV7179的通信。DM642å’ŒADV7179的接å£å¦‚图2所示。由DM642产生与I2C总线外设通信所需的时钟信å·ã€‚

3.5 视频显示模å—

TMS320DM642处ç†å™¨é›†æˆäº†3个功能丰富的视频å£VP0~VP2,æ¯ä¸ªè§†é¢‘å£åŒ…括20ä½æ•°æ®ä¿¡å·VPxD[19:0],2路时钟信å·VPxCLK[1:0]以åŠ3路控制信å·VPxCTL[2:0]。时钟信å·VPxCLK[1:0]作为视频å£å’Œå¤–部编ç ã€è§£ç 电路的åŒæ¥æ—¶é’Ÿï¼ŒæŽ§åˆ¶ä¿¡å·VPxCTL[2:0]用于视频åŒæ¥(如行åŒæ¥ã€å¸§åŒæ¥ã€åœºåŒæ¥)和视频å£ä½¿èƒ½æŽ§åˆ¶ã€‚æ¯ä¸ªè§†é¢‘å£åˆ’分为Aã€B两个通é“,æ¯ä¸ªé€šé“æ—¢å¯ä»¥é…置为视频输入å£ï¼Œä¹Ÿå¯ä»¥é…置为视频输出å£ï¼Œä½†æ˜¯Aã€B两个通é“在使用过程ä¸å¿…须没置为相åŒç±»åž‹çš„输入或输出,ä¸èƒ½ä¸€ä¸ªé€šé“é…置为视频输入,å¦ä¸€ä¸ªé€šé“é…置为视频输出。本设计ä¸ä»…用到了视频å£çš„输出功能,视频编ç 芯片ADV7179与DM642的视频å£1相连接,具体信å·çº¿è¿žæŽ¥æ–¹å¼å¦‚图2所示。

4 软件设计

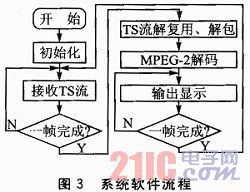

系统软件的设æ±å’Œè°ƒè¯•æ˜¯åœ¨TIå…¬å¸çš„集æˆå¼€å‘环境CCS3.3(Code Composer Studio 3.3)下完æˆçš„,系统软件æµç¨‹å¦‚图3所示。整个系统软件是在BIOS下基于RF-5(å‚考设计框架)设计的,设计得到了简化。

在进行DSPï¼BIOS任务调度å‰ï¼Œç¨‹åºè¿›è¡Œäº†ä»¥ä¸‹å‡ 个部分的åˆå§‹åŒ–:

①åˆå§‹åŒ–系统和处ç†å™¨ã€‚

◆åˆå§‹åŒ–BIOSå’ŒCSL(Chip Support Library)ï¼›

◆设置使用64 KB的二级高速缓å˜ï¼Œå¹¶å°†å…¶æ˜ 射到EMIFçš„CE0å’ŒCE1空间;

◆设置DMA的优先级åºåˆ—长度;

◆将二级高速缓å˜çš„请求优先级设为最高。

②åˆå§‹åŒ–RF-5模å—。

◆系统åˆå§‹åŒ–RF-5通é“模å—ï¼›

◆系统åˆå§‹åŒ–RF-5框架ä¸ç”¨äºŽå†…部å•å…ƒé—´é€šä¿¡å’Œä¼ 递消æ¯çš„ICCå’ŒSCOM模å—ï¼›

◆å„通é“在内部的ã€æ‰©å±•çš„å’Œä¸´æ—¶çš„å †ä¸Šå®Œæˆå»ºç«‹ã€‚

③建立输入和显示通é“。

◆建立和å¯åŠ¨ä¸€ä¸ªè¾“入通é“的实例;

◆建立和å¯åŠ¨ä¸€ä¸ªæ˜¾ç¤ºé€šé“的实例。

④建立算法实例。

◆在通é“ä¸å»ºç«‹å’Œæ³¨å†ŒTSæµè§£å¤ç”¨å•å…ƒï¼›

◆在通é“ä¸å»ºç«‹å’Œæ³¨å†ŒPES(打包基本ç æµ)解包å•å…ƒï¼›

◆在通é“ä¸å»ºç«‹å’Œæ³¨å†ŒMPEG-2解ç å•å…ƒï¼›

◆打开通é“,建立TSæµè§£å¤ç”¨ã€PES解包和MPEG-2解ç å•å…ƒçš„实例。

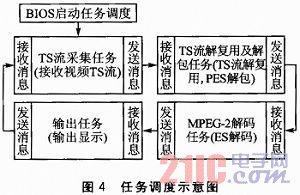

以上åˆå§‹åŒ–工作全部完æˆåŽï¼Œç³»ç»Ÿåˆ™è¿›å…¥DSPï¼BIOS渊度程åºç®¡ç†ä»¥ä¸‹çš„4个任务系统。4个任务通过RF-5çš„SCOM模å—相互å‘é€æ¶ˆæ¯ï¼Œä»»åŠ¡è°ƒåº¦ç¤ºæ„图如图4所示。

4个任务å„自实现的功能如下:

①TSæµé‡‡é›†ä»»åŠ¡ã€‚TSæµé‡‡é›†ä»»åŠ¡å®Œæˆæ•°æ®çš„采集和å˜å‚¨ã€‚在该任务ä¸ï¼ŒDSP从外部SPI接å£èŽ·å¾—一帧最新的视频图åƒTSæµï¼Œå¹¶å°†å…¶å˜å‚¨åœ¨å¤–部SDRAMä¸ã€‚TSæµé‡‡é›†ä»»åŠ¡æŽ¥ç€å‘é€æ¶ˆæ¯åˆ°TSæµè§£å¤ç”¨ã€è§£åŒ…任务,消æ¯ä¸åŒ…å«TSæµæ•°æ®æŒ‡é’ˆï¼Œç„¶åŽç‰å¾…输出任务å‘é€æ¥çš„消æ¯ä»¥ä¾¿æŽ¥æ”¶ä¸‹ä¸€å¸§TSæµæ•°æ®ã€‚

②TSæµè§£å¤ç”¨åŠè§£åŒ…任务。TSæµè§£å¤ç”¨ã€è§£åŒ…任务通过RF-5通é“实现TSæµçš„解å¤ç”¨å’ŒPES包解包。该任务当接收到TSæµé‡‡é›†ä»»åŠ¡å‘é€æ¥çš„消æ¯æ—¶è¢«æ¿€æ´»å¼€å§‹è¿è¡Œï¼ŒTSæµè§£å¤ç”¨å•å…ƒå°†TSæµæ•°æ®å°åŒ…解å¤ç”¨ï¼Œç”ŸæˆPES包,PES解包å•å…ƒå†å°†PES包解包æˆåŸºæœ¬ç æµ(ES)。这一系列过程完æˆåŽï¼Œä»»åŠ¡å‘é€æ¶ˆæ¯åˆ°MPEG-2解ç 任务,消æ¯ä¸åŒ…å«è§£åŒ…åŽESæ•°æ®æŒ‡é’ˆï¼Œç„¶åŽç‰å¾…TSæµé‡‡é›†ä»»åŠ¡å‘é€æ–°çš„消æ¯ã€‚

③MPEG-2解ç 任务。解ç 任务通过RF-5通é“实现基本ç æµES的解ç 。该任务接收到TSæµè§£å¤ç”¨ã€è§£åŒ…任务å‘é€æ¥çš„消æ¯åŽç«‹åˆ»è¢«æ¿€æ´»å¼€å§‹è¿è¡Œã€‚MFEG-2解ç å•å…ƒå°†ES解ç ,生æˆå›¾åƒæ•°æ®ï¼ŒæŽ¥ç€å‘é€æ¶ˆæ¯åˆ°è¾“出任务,消æ¯ä¸åŒ…å«å›¾åƒæ•°æ®çš„指针。解ç 任务接下æ¥ç‰å¾…接收TSæµè§£å¤ç”¨ã€è§£åŒ…任务å‘é€æ¥çš„新消æ¯ï¼Œç”¨æ¥è¿›è¡Œä¸‹ä¸€å¸§å›¾åƒES的解ç 任务。

④输出任务。输出任务接收到MPEG-2解ç 任务å‘é€æ¥çš„消æ¯åŽå¼€å§‹å¯åŠ¨è¿è¡Œï¼Œåˆ©ç”¨è¾“出驱动程åºå°†å›¾åƒæ•°æ®è¾“出到视频编ç 器ADV7179。一帧图åƒæ•°æ®æ¬è¿å®ŒæˆåŽï¼Œå‘é€æ¶ˆæ¯ç»™TSæµé‡‡é›†ä»»åŠ¡ï¼ŒæŽ¥ç€ç‰å¾…解ç 任务å‘é€æ¥çš„新消æ¯ã€‚

5 实验结果

将编译好的程åºæ–‡ä»¶é€šè¿‡FlashBurn烧写到Flashå˜å‚¨å™¨ä¸ï¼Œè¿žæŽ¥å¥½TSæµè¾“入接å£å’Œæ˜¾ç¤ºè®¾å¤‡ï¼ŒåŽ»æŽ‰ä»¿çœŸå™¨ï¼Œå¤ä½DSPç›®æ ‡æ¿ï¼Œä½¿ç¨‹åºè‡ªåŠ¨åŠ è½½è¿è¡Œã€‚实验得到的显示效果如图5æ‰€ç¤ºã€‚è§†é¢‘æ˜¾ç¤ºæ¸…æ™°æ— æŠ–åŠ¨ï¼Œè¾¾åˆ°äº†é¡¹ç›®è®¾è®¡è¦æ±‚。

结è¯

本文设计了基于TMS320DM642å’ŒADV7179的符åˆå·¥ä¸šå·¥ä½œæ¸©åº¦æ ‡å‡†çš„视频实时处ç†å’Œæ˜¾ç¤ºç³»ç»Ÿã€‚在硬件方é¢å¯¹å„主è¦æ¨¡å—分别进行了详细的设计æ述,在软件方é¢é‡ç‚¹ä»‹ç»äº†DSPï¼BIOS下å„处ç†ä»»åŠ¡çš„实现方å¼åŠå…¶è°ƒåº¦ç–略。最åŽé€šè¿‡å®žéªŒéªŒè¯äº†ç³»ç»Ÿèƒ½å¤Ÿæ£å¸¸å·¥ä½œï¼Œå¹¶ä¸”能够得到较好的显示效果。

DM642出色的图åƒå¤„ç†èƒ½åŠ›å¯ä»¥ä½¿è¯¥ç³»ç»Ÿå®žçŽ°è¾¹ç¼˜æ£€æµ‹ã€å›¾åƒå¢žå¼ºã€å›¾åƒäºŒå€¼åŒ–和滤波ç‰ä»»åŠ¡ã€‚由于本系统工作温度范围较通常的视频处ç†è®¾å¤‡å¤§ï¼Œå› 而具有更广阔的应用空间。

Led Flexible Light also called Reading Table Light, Led Bed Light , Flexible Usb Charging Light, desk portable reading light. It can be applied for the bedside, home, hotel reading lighting and can also be used as spot light for shelf lighting.

Features

-

2200k color temperature design, comfortable for sleeping, suitable reading intensity

-

High luminous efficiency, high CRI, small color difference,small angle light

-

Switch on and off by pushing the lens in the head of lights

-

With USB charging function

Parameter

Voltage 12V/24V

Power 3W

CRI >90

Efficiency 80Lm/W

Protection IP20

Beam angle 60°

USB 5V, 2A, Max 10W

Compatable driver output DC 12V/24V, 15W

FAQ:

Q1. Can I have a sample order for led light?

A: Yes, we welcome sample order to test and check quality. Mixed samples are acceptable.

Q2. What about the lead time?

A:Sample needs 3-5 days, mass production time needs 1-2 weeks for order quantity more than

Q3. Do you have any MOQ limit for led light order?

A: Low MOQ, 1pc for sample checking is available

Q4. How do you ship the goods and how long does it take to arrive?

A: We usually ship by DHL, UPS, FedEx or TNT. It usually takes 3-7 days to arrive. Airline and sea shipping also optional.

Led Flexible Light,Flexible Usb Charging Light,Led Bed Light,Reading Table Light

Shenzhen Jedver Smart Lighting Co., Ltd. , https://www.jederwell.com